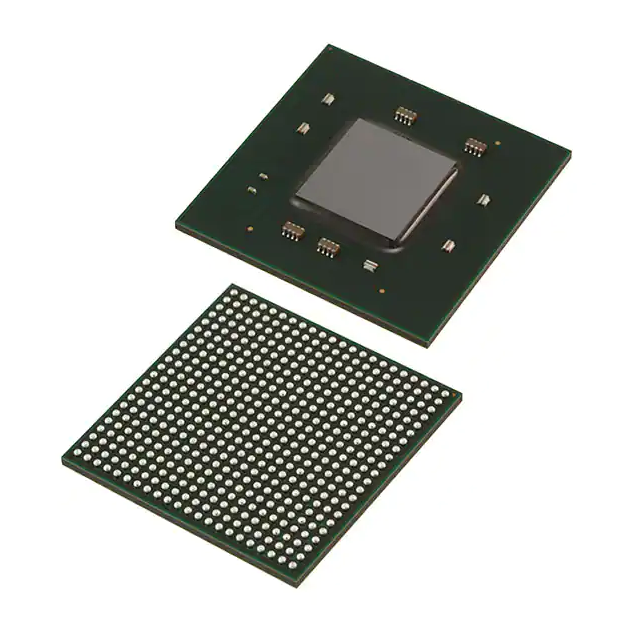

Ġdid u Oriġinali XC7A100T-2FGG484I IC Ċirkwit Integrat FPGA Qasam Programable Gate Array ad8313 IC FPGA 285 I/O 484FBGA

Attributi tal-Prodott

| TIP | DESKRIZZJONI |

| Kategorija | Ċirkwiti Integrati (ICs)Inkorporat |

| Mfr | AMD Xilinx |

| Serje | Artix-7 |

| Pakkett | Trej |

| Pakkett Standard | 60 |

| Status tal-Prodott | Attiva |

| Numru ta' LABs/CLBs | 7925 |

| Numru ta' Elementi/Ċelloli Loġiċi | 101440 |

| Bits RAM totali | 4976640 |

| Numru ta' I/O | 285 |

| Vultaġġ – Provvista | 0.95V ~ 1.05V |

| Tip ta 'Immuntar | Immonta tal-wiċċ |

| Temperatura operattiva | -40°C ~ 100°C (TJ) |

| Pakkett / Kawża | 484-BBGA |

| Pakkett tal-Apparat tal-Fornitur | 484-FBGA (23×23) |

| Numru tal-Prodott Bażi | XC7A100 |

L-użu ta 'FPGAs bħala proċessuri tat-traffiku għas-sigurtà tan-netwerk

It-traffiku lejn u minn tagħmir tas-sigurtà (firewalls) huwa kkodifikat f'diversi livelli, u l-encryption/decryption L2 (MACSec) hija pproċessata fin-nodi tan-netwerk tas-saff tal-link (L2) (swiċċijiet u routers).L-ipproċessar lil hinn mill-L2 (saff MAC) tipikament jinkludi parsing aktar profond, decryption tal-mina L3 (IPSec), u traffiku SSL encrypted bi traffiku TCP/UDP.L-ipproċessar tal-pakketti jinvolvi l-parsing u l-klassifikazzjoni tal-pakketti deħlin u l-ipproċessar ta 'volumi kbar ta' traffiku (1-20M) b'rendiment għoli (25-400Gb/s).

Minħabba n-numru kbir ta 'riżorsi tal-kompjuters (cores) meħtieġa, NPUs jistgħu jintużaw għall-ipproċessar tal-pakketti b'veloċità relattivament ogħla, iżda l-ipproċessar tat-traffiku ta' latenza baxxa, skalabbli ta 'prestazzjoni għolja mhuwiex possibbli minħabba li t-traffiku jiġi pproċessat bl-użu ta' qlub MIPS/RISC u skedar bħal dawn. ibbażat fuq id-disponibbiltà tagħhom hija diffiċli.L-użu ta 'apparat ta' sigurtà bbażat fuq FPGA jista 'jelimina b'mod effettiv dawn il-limitazzjonijiet ta' arkitetturi bbażati fuq CPU u NPU.

Ipproċessar tas-sigurtà fil-livell tal-applikazzjoni fl-FPGAs

L-FPGAs huma ideali għall-ipproċessar tas-sigurtà inline fil-firewalls tal-ġenerazzjoni li jmiss minħabba li jissodisfaw b'suċċess il-ħtieġa għal prestazzjoni ogħla, flessibilità u tħaddim b'latenza baxxa.Barra minn hekk, l-FPGAs jistgħu wkoll jimplimentaw funzjonijiet ta 'sigurtà fil-livell ta' applikazzjoni, li jistgħu jkomplu jiffrankaw ir-riżorsi tal-kompjuter u jtejbu l-prestazzjoni.

Eżempji komuni tal-ipproċessar tas-sigurtà tal-applikazzjoni fl-FPGAs jinkludu

- TTCP offload engine

- Tqabbil ta' espressjoni regolari

- Ipproċessar ta' encryption asimetriku (PKI).

- Ipproċessar TLS

Teknoloġiji tas-sigurtà tal-ġenerazzjoni li jmiss li jużaw FPGAs

Bosta algoritmi asimmetriċi eżistenti huma vulnerabbli għal kompromess minn kompjuters kwantistika.Algoritmi tas-sigurtà asimmetriċi bħal RSA-2K, RSA-4K, ECC-256, DH, u ECCDH huma l-aktar affettwati mit-tekniki tal-komputazzjoni kwantistika.Qed jiġu esplorati implementazzjonijiet ġodda ta 'algoritmi asimmetriċi u standardizzazzjoni NIST.

Il-proposti attwali għall-encryption post-quantum jinkludu l-metodu Ring-on-Error Learning (R-LWE) għal

- Kriptografija Ċavetta Pubblika (PKC)

- Firem diġitali

- Ħolqien ewlenin

L-implimentazzjoni proposta tal-kriptografija taċ-ċavetta pubblika tinkludi ċerti operazzjonijiet matematiċi magħrufa (TRNG, kampjun tal-ħoss Gaussian, żieda polinomjali, diviżjoni tal-kwantifikatur polinomjali binarju, multiplikazzjoni, eċċ.).FPGA IP għal ħafna minn dawn l-algoritmi huwa disponibbli jew jista 'jiġi implimentat b'mod effiċjenti bl-użu ta' blokki ta 'bini FPGA, bħal DSP u magni AI (AIE) f'apparat Xilinx eżistenti u tal-ġenerazzjoni li jmiss.

Din il-white paper tiddeskrivi l-implimentazzjoni tas-sigurtà L2-L7 bl-użu ta 'arkitettura programmabbli li tista' tiġi skjerata għall-aċċelerazzjoni tas-sigurtà f'netwerks ta 'tarf/aċċess u firewalls tal-ġenerazzjoni li jmiss (NGFW) f'netwerks ta' intrapriżi.