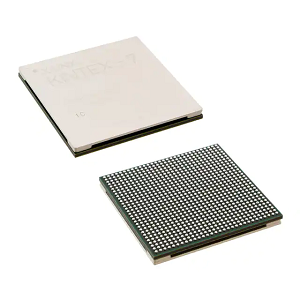

XC7K420T-2FFG901I – Ċirkwiti Integrati, Inkorporati, Arrays ta’ Bibien Programmabbli fuq il-Qasam

Attributi tal-Prodott

| TIP | ILLUSTRA |

| kategorija | Ċirkwiti Integrati (ICs)Inkorporat Arrays Programmable Gate Arrays (FPGAs) |

| manifattur | AMD |

| serje | Kintex®-7 |

| wrap | trej |

| L-istatus tal-prodott | Attiva |

| DigiKey huwa programmabbli | Mhux ivverifikat |

| Numru LAB/CLB | 32575 |

| Numru ta' elementi/unitajiet loġiċi | 416960 |

| Numru totali ta 'RAM bits | 30781440 |

| Numru ta' I/Os | 380 |

| Vultaġġ - Provvista ta 'enerġija | 0.97V ~ 1.03V |

| Tip ta 'installazzjoni | Tip adeżiv tal-wiċċ |

| Temperatura operattiva | -40°C ~ 100°C (TJ) |

| Pakkett/Djar | 900-BBGA、FCBGA |

| Inkapsulament tal-komponent tal-bejjiegħ | 901-FCBGA (31x31) |

| Numru prinċipali tal-prodott | XC7K420 |

| TIP | ILLUSTRA |

| kategorija | Ċirkwiti Integrati (ICs)Inkorporat |

| manifattur | AMD |

| serje | Kintex®-7 |

| wrap | trej |

| L-istatus tal-prodott | Attiva |

| DigiKey huwa programmabbli | Mhux ivverifikat |

| Numru LAB/CLB | 32575 |

| Numru ta' elementi/unitajiet loġiċi | 416960 |

| Numru totali ta 'RAM bits | 30781440 |

| Numru ta' I/Os | 380 |

| Vultaġġ - Provvista ta 'enerġija | 0.97V ~ 1.03V |

| Tip ta 'installazzjoni | Tip adeżiv tal-wiċċ |

| Temperatura operattiva | -40°C ~ 100°C (TJ) |

| Pakkett/Djar | 900-BBGA、FCBGA |

| Inkapsulament tal-komponent tal-bejjiegħ | 901-FCBGA (31x31) |

| Numru prinċipali tal-prodott | XC7K420 |

FPGAs

Vantaġġi

Il-vantaġġi tal-FPGAs huma kif ġej:

(1) FPGAs jikkonsistu f'riżorsi tal-ħardwer bħal ċelluli loġiċi, RAM, multiplikaturi, eċċ. Billi torganizza dawn ir-riżorsi tal-ħardwer b'mod razzjonali, jistgħu jiġu implimentati ċirkwiti tal-ħardwer bħal multiplikaturi, reġistri, ġeneraturi tal-indirizzi, eċċ.

(2) L-FPGAs jistgħu jiġu ddisinjati bl-użu ta 'dijagrammi tal-blokki jew Verilog HDL, minn ċirkwiti ta' gate sempliċi għal ċirkwiti FIR jew FFT.

(3) FPGAs jistgħu jiġu pprogrammati mill-ġdid b'mod infinit, tagħbija soluzzjoni ta 'disinn ġdid fi ftit mijiet ta' millisekondi biss, bl-użu ta 'konfigurazzjoni mill-ġdid biex tnaqqas l-overhead tal-hardware.

(4) Il-frekwenza operattiva tal-FPGA hija ddeterminata miċ-ċippa FPGA kif ukoll mid-disinn, u tista 'tiġi modifikata jew sostitwita b'ċippa aktar mgħaġġla biex tissodisfa ċerti rekwiżiti eżiġenti (għalkemm, ovvjament, il-frekwenza operattiva mhix illimitata u tista' tiżdied, iżda hija rregolata minn proċessi IC attwali u fatturi oħra).

Żvantaġġi

L-iżvantaġġi tal-FPGAs huma kif ġej:

(1) L-FPGAs jiddependu fuq l-implimentazzjoni tal-ħardwer għall-funzjonijiet kollha u ma jistgħux jimplimentaw operazzjonijiet bħal qabżiet kondizzjonali tal-fergħat.

(2) L-FPGAs jistgħu jimplimentaw biss operazzjonijiet b'punt fiss.

Fil-qosor: L-FPGAs jiddependu fuq ħardwer biex jimplimentaw il-funzjonijiet kollha u jistgħu jitqabblu ma 'ċipep dedikati f'termini ta' veloċità, iżda hemm vojt kbir fil-flessibilità tad-disinn meta mqabbel ma 'proċessuri għal skopijiet ġenerali.

Lingwi tad-disinn u pjattaformi

Apparat loġiku programmabbli huma trasportaturi tal-ħardwer li jikkonkretizzaw il-funzjonijiet stabbiliti u l-ispeċifikazzjonijiet tekniċi ta 'applikazzjonijiet elettroniċi permezz tat-teknoloġija EDA.L-FPGAs, bħala wieħed mill-apparati mainstream li jimplimentaw din it-triq, huma orjentati direttament lejn l-utent, estremament flessibbli u versatili, faċli biex jintużaw, u malajr biex jiġu ttestjati u implimentati fil-ħardwer.

Lingwa tad-Deskrizzjoni tal-Hardware (HDL) hija lingwa użata biex tiddisinja sistemi ta 'loġika diġitali u tiddeskrivi ċirkwiti diġitali, dawk ewlenin użati komunement huma VHDL, Verilog HDL, System Verilog u System C.

Bħala lingwa ta 'deskrizzjoni tal-ħardwer kollha, il-Lingwa ta' deskrizzjoni tal-ħardwer taċ-ċirkwit integrat b'veloċità għolja ħafna (VHDL) għandha l-karatteristiċi li tkun indipendenti miċ-ċirkwit tal-ħardwer speċifiku u indipendenti mill-pjattaforma tad-disinn, bil-vantaġġi ta 'kapaċità ta' deskrizzjoni fuq firxa wiesgħa, mhux dipendenti fuq apparati speċifiċi, u l-abbiltà li tiddeskrivi d-disinn ta 'loġika ta' kontroll kumplessa f'kodiċi rigoruż u konċiż, eċċ Huwa appoġġjat minn ħafna kumpaniji EDA u ġie użat ħafna fil-qasam tad-disinn elettroniku.użat ħafna.

VHDL huwa lingwa ta 'livell għoli għad-disinn taċ-ċirkwit, u meta mqabbel ma' lingwi oħra ta 'deskrizzjoni ta' ħardwer, għandu l-karatteristiċi ta 'lingwa sempliċi, flessibilità u indipendenza mid-disinn tal-apparat, li jagħmilha lingwa ta' deskrizzjoni ta 'ħardwer komuni għat-teknoloġija EDA u tagħmel it-teknoloġija EDA aktar aċċessibbli għad-disinjaturi.

Verilog HDL hija lingwa ta 'deskrizzjoni tal-ħardwer użata ħafna li tista' tintuża f'diversi stadji tal-proċess tad-disinn tal-ħardwer, inklużi l-immudellar, is-sinteżi u s-simulazzjoni.

Verilog HDL Vantaġġi: simili għal C, faċli biex titgħallem u flessibbli.Sensittivi għall-każ.Vantaġġi fl-istimolu tal-kitba u l-immudellar.Żvantaġġi: ħafna żbalji ma jistgħux jiġu skoperti fil-ħin tal-kompilazzjoni.

Vantaġġi VHDL: Sintassi rigoruża, ġerarkija ċara.Żvantaġġi: żmien twil ta 'familjarizzazzjoni, mhux flessibbli biżżejjed.

Is-softwer Quartus_II huwa ambjent ta 'disinn sħiħ b'ħafna pjattaformi żviluppat minn Altera, li jista' jissodisfa l-ħtiġijiet tad-disinn ta 'diversi FPGAs u CPLDs, u huwa ambjent komprensiv għal disinn ta' sistema programmabbli fuq iċ-ċippa.

Vivado Design Suite, ambjent ta 'disinn integrat rilaxxat mill-bejjiegħ FPGA Xilinx fl-2012. Jinkludi ambjent ta' disinn integrat ħafna u ġenerazzjoni ġdida ta 'għodod minn sistema għal livell IC, kollha mibnija fuq mudell ta' data skalabbli kondiviż u ambjent ta 'debug komuni.il Xilinx Vivado Design Suite jipprovdi FIFO IP cores li jistgħu jiġu applikati faċilment għad-disinji.